ecosnos.ru

|

ecosnos.ru |

|

|

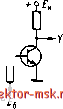

Главная Классификация и характеристики магнитофонов 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 [ 32 ] 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 мыкание (0) контакта, наличие (1) и отсутствие (0) напряжения. Цифры 1 и О являются здесь не числами, а символами. Управляющий логический элемент обычно содержит: 1. Входные элементы, воспринимающие входные сигналы от аппаратов управления или датчиков и преобразующие их в напряжение высокого и низкого уровней (сигналы О и 1). 2. Промежуточные логические элементы, преобразующие в соответствии с заданной программой работы входные сигналы (О и 1) в необходимую комбинацию выходных сигналов (также в виде О и 1). 3. Усилители, повыщающие мощность выходных сигналов. 4. Исполнительные элементы, воспринимающие вьгеодные сигналы и выполняющие функции, для которьге предназначено данное устройство. Ими являются контакторы, электромагниты, электродвигатели, индикаторные устройства и т. п. Обычно входной сигнал обозначается буквой Xj, если он равен 1 и такой же буквой с черточкой наверху (знак отрицания, инверсии) Xj, если он равен 0. Выходные сигналы чаще всего обозначаются буквами Y, Z (У, Z), исполнительные органы буквами X, Y, Z. Основные логические элементы. Основными логическими элементами являются: элемент ИЛИ, элемент И и элемент НЕ (инвертор). Элемент ИЛИ-это дизъюиктор, который должен выдавать на вькоде напряжение высокого уровня (логическую 1) тогда, когда на входах присутствует хотя бы одно напряжение высокого уровня (логическая 1), и напряжение низкого уровня, когда на входах напряжение низкого уровня (логический 0). Таблица истинности, схема элемента ИЛИ на два входа на диодах и резисторе и условное обозначение приведены на рис. 8.84, а. С применением символики алгебры логики действие этого элемента запищется в виде Y = Xj -(- Х2. Это означает, что Y = 1, когда или входной сигнал X или вхоДной сигнал Х2 равен 1. Элемент И-конъюнктор, который вырабатывает напряжение высокого уровня (логичес- кую 1) в том случае, когда напряжение высокого уровня (логические 1) поданы одновременно на все входы. Таблица истинности, схема элемента на два входа и условное обозначение приведены на рис. 8.84,6. Условная запись этой операции имеет вид Y=X,X2, т. е. Y = 1 только тогда, когда и Х;, и Х2 равны 1. Элемент (НЕ)-инвертор, который должен изменять логическое содержание сигнала на обратное, т. е. при входном напряжении низкого уровня О на выходе должно быть напряжение высокого уровня и наоборот. Таблица истинности, пример схемы инвертора на транзисторе и условные обозначения приведены на рис. 8.84, е. Сопротивление входного делителя К R2 совместно с положительным входньп>г сигналом и напряжением источника смещения -Eg задают два различных состояния транзистора, а именно: при отсутствии на входе сигнала транзистор закрыт обратным смещением от источника - Eg и на выходе получается сигнал, близкий к -t- Е,; при подаче на вход сигнала транзистор открьшается и на выходе будет сигнал, отличающийся от потенциала нуля на 0,3... 0,5 В. Это будет напряжение низкого уровня на выходе. Элемент НЕ реализует операцию логического отрицания Y = X, т. е. Y = 1 только тогда, когда х = 0. На рис. 8.85 даны таблица, пример схемы и условное обозначение логического элемента

М М 1  Рис. 8.85 X, т т т -Г Y X,

-I Кг л. т Рис. 8.84

Рис. 8.86 С=АВ*АВ

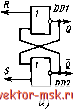

Рис. 8.87 И-НЕ. На рис. 8.86 приведена таблица, пример схемы с применением полевых транзисторов и условное обозначение логического элемента ИЛИ-НЕ. Исключительно ИЛИ В логической цепи исключительно ИЛИ сигнал на выходе появляется в том случае, когда на один вход подано напряжение низкого уровня, а на другой-высокого. Логическая функция схемы исключительно ИЛИ записывается в виде АВ -I- АВ = С. Как показано на рис. 8.87, для реализации этой функции требуются два элемента И и один элемент ИЛИ. Операция исключительно ИЛИ может быть реализована с помощью трех элементов НЕ-И следующим образом: АВ-1-АВ = АВАВ. Такое устройство называют сумматором по модулю два, так как выходная величина его равна сумме двух входных с основанием два. Рассмотрим примеры устройств, выполняемых с применением логических элементов. Переключатель капалов. На рис. 8.88 изображен двухпозиционный переключатель, с помощью С=Ах*Вх А ппп ппп . п п п п . I I . ппп п п и в] да- &Ux С=АхВх= =Ах+Вх Рис. 8.89 которого цифровые данные из каналов А или В направляются в канал С с помощью сигнала х. Когда X = 1, данные поступают из канала А, а когда X = 0-из канала В. Логическое выражение этой операции записывается в виде Ах -I- Вх = С. На выходе С появляется логическая 1 в том случае, если А и х равны 1 или если В и х равны 1. Так как хх = 0, ахихне могут одновременно принять значение 1, на выход будут проходить данные либо из канала А, либо из канала В, но никогда из двух каналов одновременно. Форма сигналов в каналах показана на рис. 8.89. Для реализации устройства требуются два элемента И и один элемент ИЛИ с инвертором. Элементы памяти па логических элементах. Элемент памяти представляет собой триггер с двумя устойчивыми состояниями с цепью управления. Цепь управления преобразует поступающую на ее входы информацию в комбинацию сигналов, действующих непосредственно на входы триггера. Триггеры подразделяются на две группы: асинхронные и синхронные (или тактируемые). Отличительной особенностью асинхронных триггеров является то, что запись информации с них осуществляется непосредственно с поступлением информационного сигнала. Информация записывается в тактируемые триггеры с информационными и тактовыми входами только при подаче разрешающего (тактирующего) синхроимпульса. Простейшей запоминающей ячейкой может служить триггер, составленный из двух элементов И НЕ (ИЛИ-НЕ). На рис. 8.90 приведена схема триггера на элементах ИЛИ-НЕ. Перекрестные связи с выходов элементов DDI и DD2 на их входы обеспечивают два устойчивых состояния всего устройства. Если на выходе DDI напряжение высокого уровня (при этом на выходе DD2-низкого), то такое состояние соответствует условному единичному Рис. 8.88 Рис. 8.90

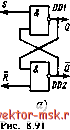

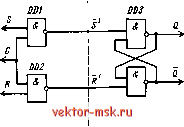

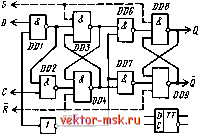

состоянию триггера (состояние 1); напряжение низкого уровня выходного сигнала на DDI (и высокое на DD2) соответствует нулевому состоянию триггера (состоянию 0). Выход элемента DDI-прямой выход триггера, и его принято обозначать буквой Q, а выход элемента DD2-инверсный выход, и его обозначают Q. Работу триггера описывает таблица переходов (рис. 8.90,6). На рис. 8.90, в приведено условное обозначение рассмотренного триггера. На рис. 8.91 приведена схема триггера на элементах И-НЕ. Так как для элементов И-НЕ достаточно напряжения нулевого уровня лишь на одном входе, чтобы на выходе было напряжение высокого уровня, триггер на элементах И-НЕ не допускает одновременной подачи на входы двух напряжений низкого уровня (первая строка таблицы). При подаче же на вход двух напряжений высокого уровня (последняя строка таблицы) состояние элементов будет определяться их предыдущим состоянием. Если же один из входных уровней О низкий, триггер может находиться в состоянии О или 1. Таким образом, по сравнению с триггером на элементах ИЛИ-НЕ в этом триггере мы имеем инверсные входы, что отмечено кружками на его графическом обозначении. Асихронные триггеры с установочными входами изменяют свое состояние сразу после изменения входных уровней. Это не всегда удобно, поэтому в триггерах часто применяют расширенную логику на входе. Такие триггеры управляют-  Схема управления л DDI -Ш9 ВдЗ Запонинан)ш,ая ячейка {RS-триггер) ся синхронизирующими сигналами, которые определяют моменты приема триггером входной информации. Схема синхронного RS триггера приведена на рис. 8.92. Она содержит триггер на элементах И-НЕ (рис. 8.90, а, правая часть) и дополнительную цепь управления на элементах DDI и DD2 (рис. 8.90, а, левая часть). Пока отсутствует сигнал синхронизации С, допустимы любые изменения сигналов S и R - они не смогут воздействовать на триггер. С момента же подачи синхронизирующего сигнала входные уровни S и R могут воздействовать на триггер. Поэтому во время подачи сигналов синхронизации недопустимо изменение входных уровней. Рассмотренный триггер работает по таблице переходов, показанной на рис. 8.90,6, а его условное графическое изображение дано на рис. 8.90, е. В общем случае триггеры могут иметь один, два и более управляющих входов. D триггер имеет один логический вход D, состояние которого с каждым синхронизирующим импульсом передается на выход, т.е. выходные сигналы представляют собой задержанные входные сигналы (см. таблицу состояний на рис. 8.93). Таким образом, D триггер-это элемент задержки входных сигналов на один такт. Т-триггер также имеет один логический вход-Т. Если на этот вход подано напряжение высокого уровня, то с каждым синхронизирующим импульсом триггер будет переходить в противоположное состояние, а если на входе напряжение низкого уровня, то триггер остается в прежнем состоянии (см. таблицу состояний на рис. 8.93). Таким образом, Т триггер реализует счет по модулю два. JK триггер имеет два входа, которые называются здесь J и К. Сигнал по входу J устанавливает триггер в состояние 1, а по входу К-в 0. Если на оба входа одновременно подать напряжения высокого уровня, то триггер с приходом каждого синхронизирующего импульса изменяет свое состояние на противоположное (см. табл. состояний на рис. 8.93). На рис. 8.94 показана логическая структура D-триггер

ЗК-триггер Рис. 8.93

Рис. 8.94  |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||